30분 응답, 1시간 엔지니어링 응답, 24시간 기술 지원, 고객 대기 시간 절약, 제품 개발 및 생산 주기 단축, 제품 출시 시간 절약, 제품 시장 공략 시간 단축

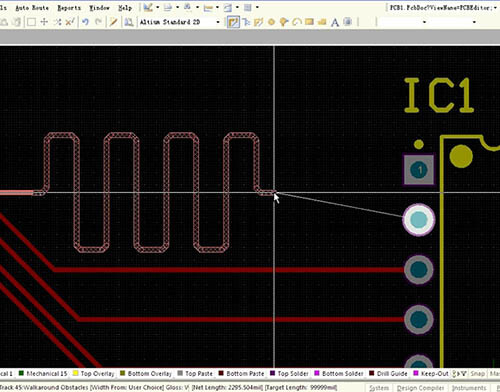

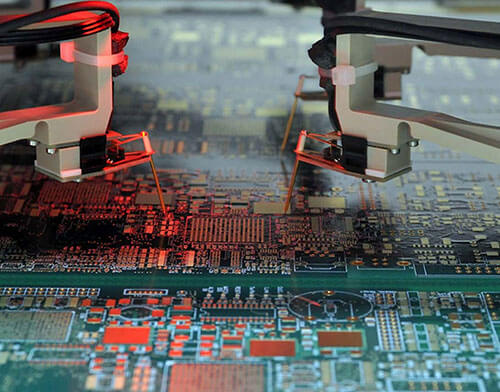

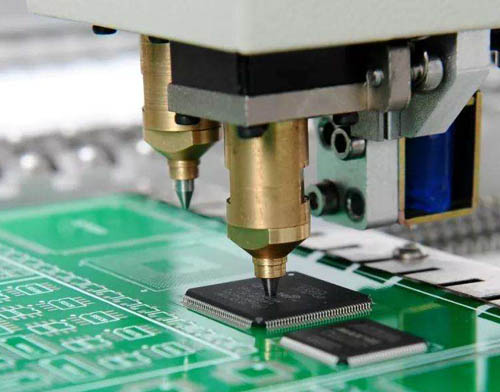

10여년의 발전을 거쳐 우리는 해마다 성장하여 기술과 생산능력을 증가시켰다.PCB 기술은 표준 PCB부터 RF 회로, 마이크로파 회로 기판, 다중 계층 PCB, 강유 PCB, HDI PCB, IC 기판, IC 테스트 기판, PCBA 조립에 이른다.

파트너의 지지와 신뢰는 앞으로 나아가는 원동력입니다.우리는 고객과 윈윈할 수 있는 업무를 찾고 있다.우리 회사 문화에는 크고 작은 고객이 없다.항상 최선을 다해 양질의 서비스를 제공하는 것이 우리의 목표이다.

Isola, 파나소닉, TUC, ITEQ, 세이지, KB, Rogers, Arlon, Taconic, 두산, 미쓰비시 가스, 듀폰 등 PCB 소재 공급업체를 광범위하게 선택

재고 재료: FR408, 370HR, TU872, RO4350B, RO4003C, RT5880, RO3010, RO3003, RF35, TLY-5, 메가 유럽 4, 메가 유럽 6, S1000-2, IT180, F4BM PCB 프로토타입 재료.

FR-4 PCB, 다중 레이어 회로 기판, HDI PCB, 세라믹 PCB, PTFE 인쇄 회로 기판, 하이브리드 회로, Teflon PCB, RF PCB, Rogers PCB를 지원합니다.고급 PCB ERP 추적 관리 시스템은 납품 시간에서 업계를 선도하고 있으며 PCB의 정시 납품률은 95% 를 넘는다.

엄격한 품질 관리 시스템은 우리를 중국에서 가장 경험 많은 인쇄 회로 기판 제조업체 중 하나로 만들었으며 10 년 이상의 역사를 가지고 있습니다.PCB 공장은 iPCB PCB 시제품을 전문적으로 제조하며, IPC 3단계 표준은 고객의 요구에 따라 선택할 수 있다.

iPCB는 선후로 전 세계 1만여개 첨단과학기술연구개발, 제조 및 서비스회사와 합작하였다.그 제품은 통신회로, 공업제어회로기판, 궤도교통PCB판, 의료전자PCB, 컴퓨터PCB, 반도체기판, 자동차전자PCB 등 인쇄회로기판 분야에 응용된다.iPCB는 또한 전 세계 60여 개국에 자원을 공급하는 원스톱 PCB-PCBA 조립 제조를 제공한다.

2024-12-27

2021-12-13

2023-02-24