Bugünlerde CMOS teknolojisi, FPGA aygıtının çoklu I/O arayüzleri olmasına izin verir. Aynı zamanda, son yıllarda, düşük güç tüketimi yüksek hızlı I/O arayüzlerinin en önemli konsepti olmaya başladı. Elektrik tüketiminin en etkili yolu voltajı azaltmak ve voltajı azaltmak, I/O arayüzü tarafından izin verilen daha küçük bir ses margini sonucunda olacak. Bu yüzden FPGA kullanıcıları sistem seviyesi sinkron değiştirme sesini (SSN) çip, paket ve PCB çevresinde hesaplamak için çok gerekli.

Bu makale sistematik olarak FPGA çıkış buferinden sebep olan SSN'e odaklanan SSN'i tanıtır. Bu tür sesi genellikle eşitlendirme çıkış sesi (SSO) denir, giriş buferinden sebep olan SSN'den farklı. Bu makale sistem seviyesi SSO'nun sebeplerini tanıtır ve düzlüklü sistem seviyesi SSO modelleme metodu teklif ediyor. Aynı zamanda, bu madde SSO modelini frekans alanı ve zaman alanı ölçümleri ile nasıl birleştireceğini açıklıyor ve SSO'yu azaltmak için birçok PCB tasarım metodlarını veriyor.

Sistem seviyesi SSO'nun oluşturma mekanizması

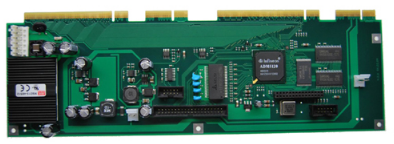

FPGA ile olan PCB, aktif devreler içeren bir çip parçasına bölünebilir, izleri destekleyen pasif komponentler ve FPGA ile dışarıdaki bağlantıları sağlayan devre tahtası parçasıdır. Bu tür sistemde, çip içerisindeki ses özelliklerini anlamak zor. Bu yüzden, FPGA ile bağlantılı PCB izlerinin yakın ve uzak ucundaki SSO'yu hesaplamak çok değerlidir. SSO'ya sebep eden iki ana faktör var: elektrik dağıtım ağının (PDN) impedance ve değişim I/O arasındaki karşılaşma induktans bağlantısı.

Sistem görüntüsünden PDN, CMOS devreleri için güç sağlayan wafer seviyesi, paket seviyesi ve tahta seviyesi komponentleri içeriyor. CMOS çıkış sürücü devrelerin belli bir sayısı aynı zamanda çalıştığı zaman, büyük bir akışı PDN'in induktiv devre elementlerine hemen akışacak, delta-I voltaj düşürmesine neden olur. Bağlantı yapıları, PCB'deki güç çözücü topların üzerindeki toplar ve güç vüyaları gibi parazitik incelemeler oluşturur. Bu hızlı değiştirme akışı da enerji/yeryüzü uçak çifti arasında radial elektromagnet dalgalarını heyecan verir. Elektromagnetik dalgalar PCB'nin planlama kenarından, enerji/yeryüzü uçağı arasındaki rezonans oluşturuyor ve voltaj fluksiyonlarına sebep ediyor.

SSO'nun başka bir önemli sebebi, özellikle çip paketi/PCB kenarındaki karşılaşma induktans bağlantısıdır. Çip BGA paketi üzerindeki soldaş topları ve PCB'deki viallar sıkı bir çeşit kablo yapısına ait. Her I/O solder topu ve eşleşik PCB aracılığıyla ve en yakın topu solder topu ve topu kapalı bir döngü şeklinde oluşturuyor. Çoklu I/O portların durumu aynı zamanda değiştiğinde, geçici I/O akışları bu sinyal dönüşünün arasından akışlar geçiyor. Bu geçici I/O akışı, yakın sinyal döngülerine saldırır ve güç gürültüsünü neden eden zamanlı değişikli manyetik alanı oluşturacak.

Mükemmel bir SSO modeli SSO'nun temel formasyon mekanizmasını düşünebilir. PCB'lerde SSO'yu tahmin etmek için katlı bir model. Çip seviyesinde, ihtiyacımız olan bir çıkış buferi modeli, enerji hatlarının ve sinyal hatlarının sınırlı kompleksitede tam bir dağıtımı sağlayabilir. Paketleme seviyesinde, basit olarak, modelleme araçları PDN modelini ve sinyal bağlama modelini almak için kullanılabilir, fakat PDN ile sinyal bağlama modelinin etkileşimi dikkatli düşünmeli. Bu iki model köprü olarak hareket ediyor, çip paketinin sonunda çıkış buffer modelini ve solder topu sonunda PCB seviye modelini bağlayıyor. PCB'nin PDN modeli genelde enerji/yeryüzü uça ğı ve üzerindeki büyük kapasitet/dekorasyon kapasiteleri dahil eder. PCB'nin sinyal bağlama modeli farklı sinyal katları üzerinde sıkı bir dizi aracılığıyla birleştirilmiş ve serbest bağlı sinyal izleri dahil eder. Bu iki PCB seviye modellerinin etkileşimli etkileşim etkisi, PCB'de bir dizi aracılığıyla görünüyor. Buradan induktif kısıtlık konuşması PDN model in in gürültüsünü getirir ve delta-I gürültüsünün I/O sinyalinin kalitesini azaltır. Bu hiyerarşik modelleme metodu simülasyon doğruluğunu mantıklı tutuyor ve aynı zamanda bu karmaşık sistemlerin hesaplama etkiliğini geliştirir.